拼接處理器技術架構分析

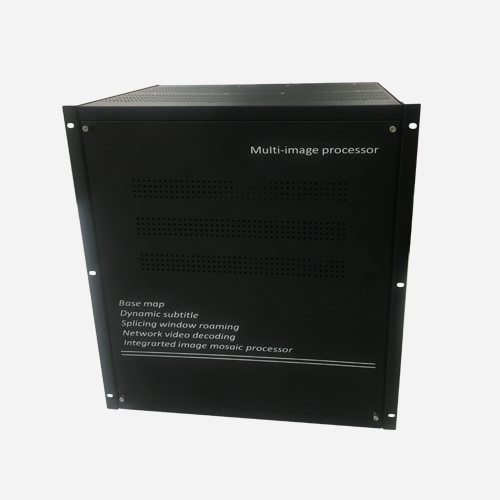

拼接處理器以其獨特的優勢,作為顯示拼接系統的核心設備之一,可以實現圖像的疊加,分辨率的調整,多個信號源的分割,任意開窗、漫游、縮放及疊加等功能。拼接處理器的作用就是實現多個顯示單元的拼接顯示,目前的拼接處理器技術架構主要分為X86架構拼接處理器,FPGA架構拼接處理器和分布式架構拼接處理器,下面我們就來詳細的分析一下這幾種架構之間的區別。

X86架構拼接處理器

這種處理器的輸出基本上采用的是多屏顯卡設備,具有多種接口,多屏顯卡的數據交換。隨著解碼器技術的發展,X86架構拼接處理器能夠直接接入IP網絡信號并經解碼后顯示輸出。X86架構拼接處理器采用windows系統設計,對于系統的穩定性依賴比較大,Windows系統的各種問題都會影響到X86架構拼接處理器的穩定性。X86架構拼接處理器適合中小規模和少量解碼需求的項目。

FPGA架構拼接處理器

采用FPGA集成電路技術設計的FPGA架構拼接處理器通過輸入輸出板卡完成數據的交換,負責信號的分割等處理和控制。可以通過IP解碼板完成對IP網絡信號的解碼,FPGA架構拼接處理器能夠滿足大部分項目需求,但不適合有大量網絡信號的應用。

分布式架構拼接處理器

分布式架構拼接處理器采用嵌入式編解碼芯片設計,各種信號數據及控制命令的傳輸通過網絡交換機完成,對于解碼編碼技術的要求較高。

以上是關于拼接處理器技術架構分析,不管哪種拼接處理器技術架構,對于實際的應用需要根據具體的需求來進行選擇。

- 上一篇:液晶拼接處理器該如何選擇呢?選購知識匯總

- 下一篇:液晶顯示屏用到拼接處理器的原因

服務熱線|

服務熱線|